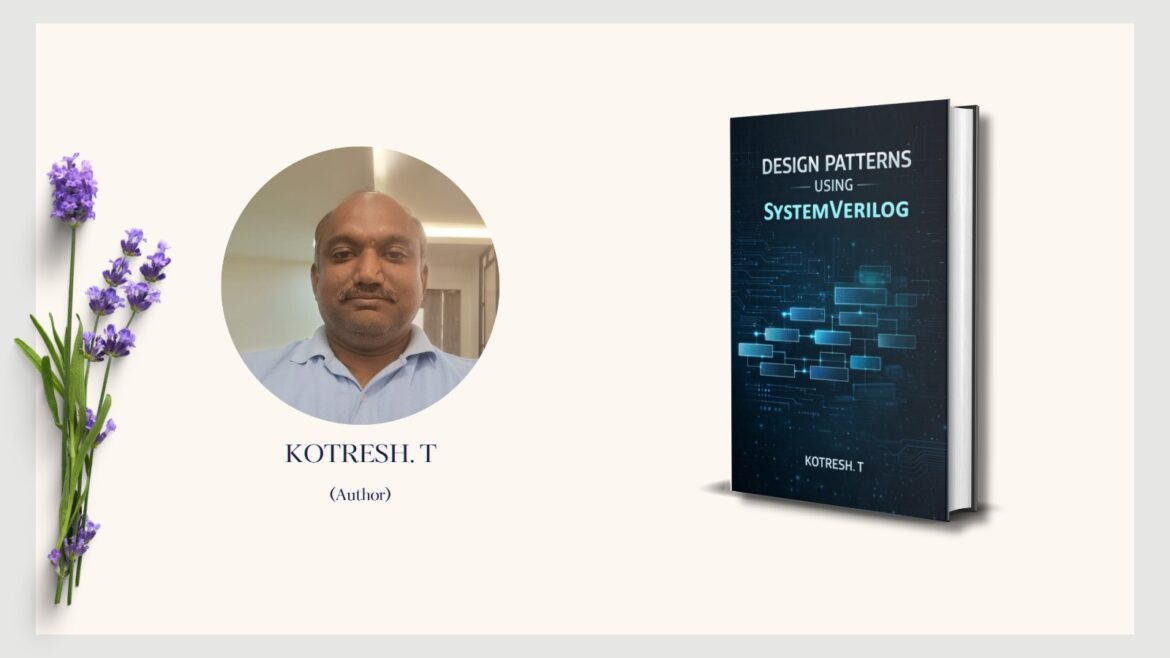

Kotresh T, the author of Design Patterns Using SystemVerilog, brings forward a thoughtful and much-needed perspective in the field of hardware verification by addressing a gap that many engineers encounter but often struggle to articulate. In an industry where the Universal Verification Methodology (UVM) has become the standard framework, there remains a persistent challenge: understanding not just how UVM works, but why it works the way it does. This book is a response to that challenge, grounded in both practical experience and a deep appreciation of foundational concepts.

With a background rooted in verification engineering, Kotresh T observed that many professionals rely heavily on using UVM components without fully grasping the design principles that shape them. This often leads to a mechanical approach to verification, where engineers replicate structures and patterns without understanding their intent or flexibility. Over time, such an approach can limit innovation, reduce efficiency, and create unnecessary complexity in testbench development. Recognizing this, the author set out to create a resource that connects the dots between software design patterns and their application in hardware verification.

At the heart of this work is the idea that UVM is not just a collection of classes and utilities, but a framework built upon well-established design patterns. These patterns—commonly used in software engineering—serve as the backbone of scalable, reusable, and maintainable systems. However, in the context of hardware verification, they are often hidden beneath layers of abstraction, making them less accessible to practitioners. Kotresh T’s approach is to bring these patterns to the forefront, explaining them in a clear and relatable manner while demonstrating how they are embedded within UVM.

One of the defining features of the book is its emphasis on clarity and application. Rather than presenting design patterns as abstract concepts, the author anchors each pattern in real verification scenarios. Through carefully crafted examples, readers are guided step-by-step from understanding a pattern’s intent to seeing its practical implementation in SystemVerilog and UVM. This method not only demystifies complex ideas but also empowers readers to apply them confidently in their own projects.

Kotresh T also highlights the importance of developing a design-oriented mindset. In verification, challenges often arise that cannot be solved by simply following templates or reusing existing code. Instead, they require thoughtful structuring, adaptability, and a clear understanding of system behavior. By learning design patterns, engineers can approach problems with a toolkit of proven solutions, enabling them to build testbenches that are both robust and flexible. This shift from ad-hoc coding to structured design thinking is one of the key messages the author conveys throughout the book.

Another important aspect of the author’s work is its inclusivity across experience levels. For beginners, the book serves as an entry point into the deeper layers of UVM, offering insights that go beyond syntax and basic usage. It helps new learners understand the rationale behind commonly used constructs, making their learning journey more meaningful and less dependent on trial and error. For experienced engineers, the book provides an opportunity to reflect on existing practices, identify patterns they may already be using intuitively, and formalize them into a more systematic approach.

Kotresh T also addresses the practical challenges faced in modern verification environments, such as scalability, maintainability, and collaboration. As projects grow in complexity, the need for well-structured and reusable verification components becomes critical. Design patterns play a crucial role in achieving this, and the author illustrates how their correct application can significantly improve productivity and code quality. By aligning theoretical concepts with real-world demands, the book remains grounded and relevant to industry needs.

Beyond the technical content, what stands out in the author’s approach is a clear intent to educate and empower. The writing reflects a deep understanding of the struggles faced by verification engineers, as well as a genuine effort to make complex ideas accessible. The explanations are structured in a way that encourages curiosity and exploration, rather than overwhelming the reader with jargon or unnecessary detail.

In a field that continues to evolve rapidly, the ability to adapt and think critically is essential. Kotresh T’s Design Patterns Using SystemVerilog contributes to this by equipping readers with not just knowledge, but a way of thinking. It bridges the gap between theory and practice, between software principles and hardware implementation, and between learning and application.

Ultimately, the author’s work serves as a reminder that strong foundations lead to better innovation. By understanding the principles that underpin UVM, engineers can move beyond simply using the framework to truly mastering it. Through this book, Kotresh T offers a pathway toward that mastery, making it a valuable addition to the library of anyone involved in hardware verification.